The World's First

EMPATHIC

PROCESSING

UNIT

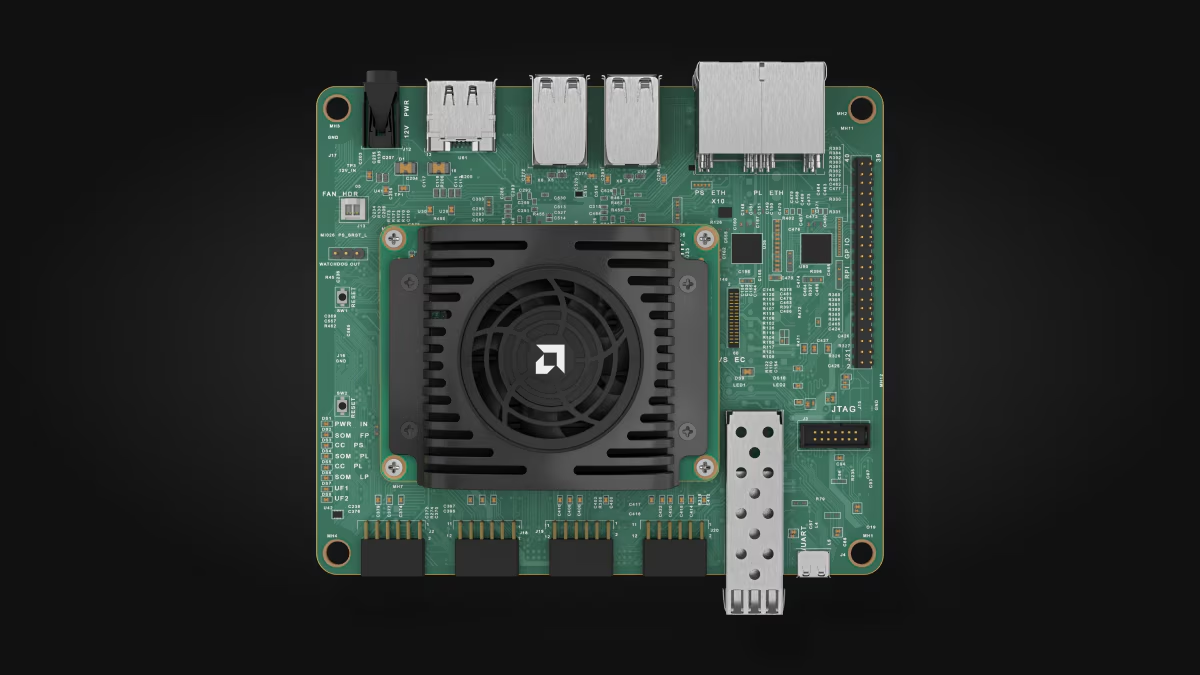

Alignment isn't trained. It's built into the silicon. The VORTICON EPU implements genuine computational pain that the model perceives and learns from.